- 您现在的位置:买卖IC网 > Sheet目录1245 > SPI-324P-O4-N1 (Lattice Semiconductor Corporation)IP PHY LAYER BRIDGE SPI3-4 ORCA4

�� �

�

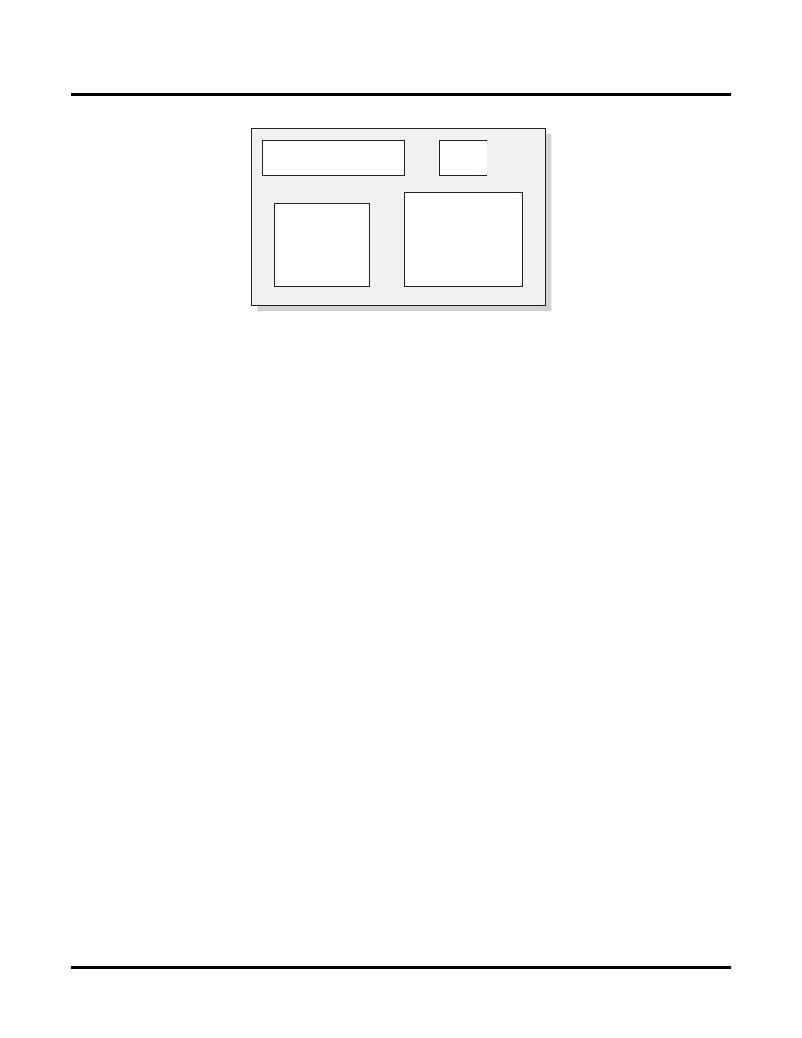

Quad� SPI-3� to� SPI-4� Link� Layer�

�Lattice� Semiconductor�

�Figure� 10.� Quad� SPI-3� to� SPI-4� Link� Layer� Bridge� Top-Level� Application�

�Bridge� Core� User’s� Guide�

�ORCA� 4� sysBUS� Model�

�ORSPI4�

�Model�

�PLL�

�Quad� SPI-3� to� SPI-4�

�Link� Layer� Bridge�

�Core�

�Black� Box� Consideration�

�Since� the� core� is� delivered� as� a� gate-level� netlist,� the� synthesis� software� will� not� re-synthesize� the� internal� nets� of�

�the� core.� For� more� information� regarding� Synplify’s� black� box� declaration,� refer� to� the� Instantiating� Black� Boxes� in�

�Verilog� section� of� the� Synplify� Reference� Manual.�

�Synthesis�

�The� following� sections� provide� procedures� for� synthesizing� the� Quad� SPI-3� to� SPI-4� Link� Layer� Bridge� Core� IP�

�solution� with� the� Synplicity� Synplify� and� LeonardoSpectrum� synthesis� tools,� which� are� included� in� the� Lattice�

�ispLEVER� software.� These� procedures� generate� an� EDIF� netlist� containing� the� Quad� SPI-3� to� SPI-4� Link� Layer�

�Bridge� core� as� a� black� box.�

�Synthesis� Using� Synplicity’s� Synplify�

�To� synthesize� the� Quad� SPI-3� to� SPI-4� Link� Layer� Bridge� solution� Synplicity’s� Synplify� in� one� step,� go� to� the� direc-�

�tory� “eval\synthesis\synplicity”� and� enter� “run_syn.bat”� (for� PC).� A� top-level� EDIF� for� the� application� will� be� pro-�

�duced.� Users� may� use� run_syn.bat� as� a� guide� and� template� if� they� are� creating� their� own� unique� system-level�

�project� solution.�

�The� following� step-by-step� procedure� may� also� be� executed.� Note� that� the� step-by-step� ?ow� results� vary� from� those�

�obtained� with� the� scripted� ?ow� due� to� possible� small� differences� in� options� between� both� ?ows.�

�1.� Create� a� new� working� directory� for� synthesis.�

�2.� Launch� the� Synplify� synthesis� tool.�

�3.� Start� a� new� project� and� add� the� speci?ed� ?les� in� the� following� order:�

�source/synplicity� /orca4_synplify.v�

�source/top/qspi3_link_params.v�

�source/synplicity/rfclk_pll_bo.v�

�source/synplicity/rfclk_hpll_bo.v�

�source/synplicity/mycore.v�

�source/synplicity/sysbus_fpsc.v�

�source/top/spi_324l_o4_1_001.v�

�source/top/fpga_io.v�

�source/top/orspi.v�

�4.� In� the� Implementation� Options� select� the� ORCA� Series� 4� technology,� the� O4E06� part,� speed� grade� -2� and�

�package� BA352.� Note� that� these� options� are� acceptable� since� synthesis� targets� the� Series� 4-based� FPGA�

�array� of� the� device.�

�5.� Specify� an� EDIF� netlist� ?lename� and� EDIF� netlist� output� location� in� the� Implementation� Options.� This� top-level�

�EDIF� netlist� will� be� used� during� Place� and� Route.�

�19�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SPN02SVBN-RC

CONN JUMPER SHORTING 2MM GOLD

SPN02SVEN-RC

CONN JUMPER SHORTING 2MM GOLD

SPN02SXCN-RC

CONN JUMPER SHORTING 2MM GOLD

SPT711XPFCE

CARD TELEPHONY FARM CRD 711X

SPUSB1AJT

SURGE SUPPRESOR USB 12OHM SC70-6

SR-5H-6.3A-BK

FUSE 6.3A 250VAC RADIAL SLOW

SR1K20M155X

VARISTOR 20VRMS W/RFI SUPP RAD

SRP120LF

POLYSWITCH PTC RESET 1.2A STRAP

相关代理商/技术参数

SPI-333-34AB

制造商:SANYO Semiconductor Co Ltd 功能描述:

SPI-335-34

制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Ultraminiature photoreflector (single-transistor type)

SPI-336-99-T1

制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Ultraminiature photoreflector supporting reflow soldering Single transistor type

SPI3501UH

制造商:SPI 制造商全称:SPI 功能描述:350 Watts EPS12V 1U Switching Power Supply

SPI3501UH-B204

制造商:Sparkle Power Inc 功能描述:POWER SUPPLY,SWITCHING,ENCLOSED,1U,350 WATT,ATX/EPS,PFC,(2)1

SPI350ACA8

制造商:SPI 制造商全称:SPI 功能描述:350 Watts, ATX Switching Power Supply

SPI350ACAG

制造商:SPI 制造商全称:SPI 功能描述:350 Watts ATX12V 2.3 Switching Power Supply Meet 2010 ErP

SPI350GLN

制造商:Sparkle Power Inc 功能描述:POWER SUPPLY,SWITCHING,ATX,350 WATT,ATX12V 2.2,PFC,(2)12VDC@